- 1. Questions from previous assignments you skipped.

- 2. Examples paper 3 (all questions)

- 3. Seven-segment displays are frequently used to display numeric digits and certain letters. You have been asked to design a display that continuously cycles through the first 8 numbers in the Fibonacci sequence in base 16 (i.e., 0, 1, 1, 2, 3, 5, 8, D) using the following number/letter shapes below:

## 0 12345678986cdEF

- (a) Compare the advantages of designing using one-hot state encoding versus sequential state encoding.

- (b) Suppose you elect to solve this problem using one-hot state encoding. Describe your state encoding. In particular, explain how many state bits are required.

- (c) Provide an identifier for each state bit in your assignment scheme. What is the combinational logic required for the output driving the bottom left segment of the display (i.e, the one highlighted in black below) in terms of your state bit identifiers?

- 4. Consider a computer architecture using the following 8-bit instruction format for a left-shift-by-one operation.

## 00101 | rrr |

where the five most-significant bits indicate the left-shift operation and the three least-significant bits (i.e., "rrr") specifies the register to apply the shift to. The left-shift-by-one instruction shifts the contents of the specified register to the left by one bit and writes the result back into that same register.

- (a) What does the instruction 0x2A do?

- (b) Sketch a circuit that implements a left-shift-by-one for an 8-bit number if an input L is asserted. If L is not asserted then the circuit's output should match the input. Feel free to use any of the logic elements covered in the lecture notes.

- (c) Is this particular computer's architecture limited to a maximum of 8 registers? Justify your answer.

- 5. The lecture notes show an example of a CMOS NAND gate with two inputs. However, many of the boolean functions discussed in lecture and in the assignments require logic gates with 3 inputs.

- (a) Draw a CMOS NAND gate with three inputs.

- (b) Draw a NMOS logic NOR gate with three inputs.

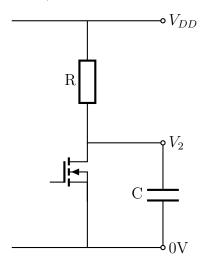

- 6. A capacitor C is connected between the source and drain terminals of the MOSFET. After the MOSFET turns OFF at t = 0, the output signal  $V_2$  as a function of time t is given by  $V_2 = V_{DD}(1 e^{-t/RC})$ . Assume that prior to t = 0, the MOSFET is ON and  $V_2 = 0$ V.

- (a) If R=500 $\Omega$ , and C=0.01 $\mu$ F how long does it take  $V_2$  to reach 80% of its maximum value?

- (b) If the output of a logic gate takes a long time to reach its maximum or minimum value, why is that disadvantageous?

- (c) To reduce the rise-time you computed in part(a) you can reduce the value of the resistor. What value of R would you need to halve the time it takes for  $V_2$  to reach 80% of its maximum value?

- (d) At some later time, the MOSFET turns back ON. When the MOSFET is on, the voltage difference between the source and drain of the transistor

$V_{DS} = 120$ mV and the current through the transistor  $I_{DS} = 80$ mA. Using the resistance you calculated in part (b), how much power is dissipated in the resistor when the transistor is ON?